http://www.sgbauonline.com

## B.E. Fourth Semester (Electronics & Telecommunication) (New)

Digital Electronics: 4 ET 04

P. Pages: 2

http://www.sgbauonline.com

AU - 2590

| * 0 9 6 9 *                             | Max. Marks: 80 |

|-----------------------------------------|----------------|

|                                         |                |

| ~ · · · · · · · · · · · · · · · · · · · |                |

| Time       | e :     | Max. Ma                                                                                                                                                                                                                                                                                          | rks: 80 |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|            | Not     | es: 1. All question carry equal marks.  2. Answer three question from section A and three question from section B.  3. Assume suitable date wherever necessary.  4. Illustrate your answer necessary with the help of neat sketches.  5. Use of pen Blue/Black ink/refill only for writing book. |         |

| 1.         | a)      | Explain in brief Transistor-Transistor logic (TTL) circuit with active pull up arrangements. Verify the logic operations given by TTL.                                                                                                                                                           | 7       |

|            | b)      | Perform the following.  i) Convert (1011011) <sub>2</sub> to Gray code  ii) Convert (28F) <sub>16</sub> to octal  iii) (75) <sub>10</sub> - (57) <sub>10</sub> by 2's complement method.                                                                                                         | 7       |

|            |         | OR                                                                                                                                                                                                                                                                                               |         |

| 2.         | a)      | Minimize the following logical expressions by Boolean Algebra<br>i) $B \oplus (B \oplus AC) = AC$                                                                                                                                                                                                | 8       |

|            |         | ii) $ABC + BCD + \overline{ABC} = BC + BD$                                                                                                                                                                                                                                                       |         |

|            | b)      | Explain the following characteristics of digital IC's.  i) Noise Margin  ii) Figure of merit  iii) Fanin and Fanout                                                                                                                                                                              | 6       |

| 3.         | a)      | Minimize the following logic function and realize using NAND gates only. $f_1(A, B, C, D) = \Sigma m(1,3,5,8,9,11,15) + d(2,13)$                                                                                                                                                                 | 7       |

|            | b)      | Design the combinational circuit for full adder and implement it using suitable gates.                                                                                                                                                                                                           | 6       |

|            |         | OR                                                                                                                                                                                                                                                                                               |         |

| 4.         | a)      | Design and explain one digit BCD adder circuit using 4-bit adder IC 74LS83 and require gates. Explain with the help of suitable example.                                                                                                                                                         | ed 7    |

|            | b)      | Design binary to gray cod converter circuit using suitable gates.                                                                                                                                                                                                                                | 6       |

| 5.         | a)      | Implement the following logical expression using 8:1 MUX $F = \Sigma m \ (0,1,2,3,4,10,11,14,15)$                                                                                                                                                                                                | 7       |

|            | b)      | Design 5-line to 32 line decoder circuit using 4-line to 16-line decoders and suitable gate                                                                                                                                                                                                      | e. 6    |

|            |         | OR                                                                                                                                                                                                                                                                                               |         |

| 6.         | a)      | Design 5-bit comparator using single 7485 IC and suitable gate. Also explain its operation.                                                                                                                                                                                                      | 7       |

|            | b)      | Compare ROM, PLA and PAL                                                                                                                                                                                                                                                                         | 6       |

| <b>A</b> 1 | 11 - 24 | 90                                                                                                                                                                                                                                                                                               | oτo     |

AU - 2590

i

P.T.O

8

13

8

5

7

- 7. a) What is Race around condition? How it is overcome? Explain master-slave J-K flip flop with proper table.

- b) Design 4-bit parallel in serial out right shift register using D-Flip Flops and suitable gates. 6

OF

- 8. a) State differences between synchronous and asynchronous counters. 5

- b) Design 2-bits asynchronous up counter using negative edge triggered T-Flip Flops and explain its operation with proper wave forms.

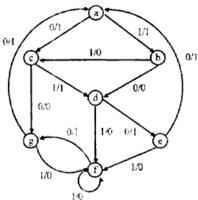

- 9. a) Obtain reduced state table and reduced state diagram for the sequential machine whose state diagram is shown below.

b) Draw the state diagram and state table for a Moore type sequence detector to detect the sequence 110.

OR

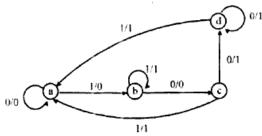

Design a clocked sequential circuit using T-Flip Flops and suitable gates for the state diagram given below.

11. a) Explain in brief-

http://www.sgbauonline.com

- i) PROM

- iii) EEPROM

- ii) EPROM

- iv) NVRAM

- b) Explain the working of dynamic RAM cell.

OR

- 12. a) Explain the read cycle timing parameters of a memory using proper timing diagram.

- b) With neat circuit diagram explain the operation of bipolar static RAM cell.

\*\*\*\*\*

2

AU - 2590